Granite River Labs, GRL

Fred Chen 陳頌揚

安全數位卡(Secure Digital Memory Card,SD Card)是一種普遍被廣泛運用於攜帶型裝置的記憶卡,例如數位相機、筆記型電腦、平板電腦、行動電話、掌上型遊戲機及電子書等。SD Card 的特點在於體積小、攜帶方便,從 2000 年所推出的 Version 1.01 到如今 8.0,SD Card 的誕生已經超過 20 年,資料儲存容量從一開始的 8MB 到 128TB,最高資料存取速度從 12MB/s 達到 985MB/s,成為市場上消費性電子產品普及使用的記憶體儲存裝置。

概述

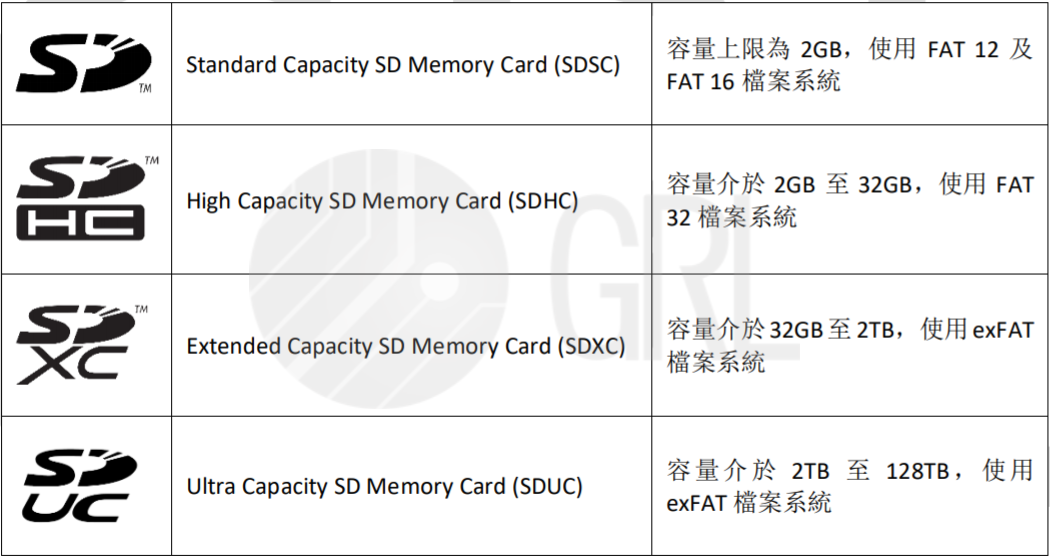

SD Card 共分為四種標準容量,他們所使用的檔案系統以及 SD 標示如下:

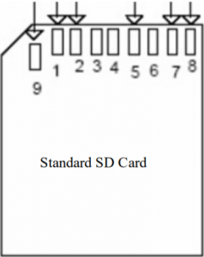

SD Card 發展至今規格版本已到 8.0,目前市面上被民眾廣泛使用的 SD Card 規格版本為 3.01 以及 4.0,因此此篇內容為 3.01 及 4.0 規格之說明。SD 3.01 其一排針腳(圖 1)除了支援基本的匯流排速度預設模式 (12.5MB/s), 及高速模式 (25MB/s) 其工作電壓為 3.3V,更支援了工作電壓為 1.8V 的 SDR25 (25MB/s)、SDR50 (50MB/s)、SDR104 (104MB/s)、DDR50 (50MB/s) 模式,此匯流排介面也命名為 UHS (Ultra High Speed)-I。SDR (Single Data Rate) ,為一個週期裡能擷取一次資料,即一個 bit,而 SD Card 有四條資料線進行傳輸所以一個週期裡可以傳 4bit,如果一秒能傳輸最高速率為 50MB/s 其最大頻率上限則為 100MHz。DDR (Double Data Rate) 為一個週期裡能擷取兩次資料,能傳輸 8bit,故傳輸最高速率會等於最大頻率上限。

UHS-I 在 SDIO 模式下可以使用四根數據線進行傳輸 (4-bits Data) 其使用到的針腳為 1、7、8、9 (DATA0-DATA3),若在不支援四線傳輸的狀況下會使用單跟線(引腳 7 DATA0)進行傳輸。針腳 2 為命令 (CMD) 用於 HOST 端與 DEVICE 端傳輸溝通時所使用的針腳。針腳 5 為時鐘線 (CLK)。詳細說明可參考下表 1。

圖 1

表 1

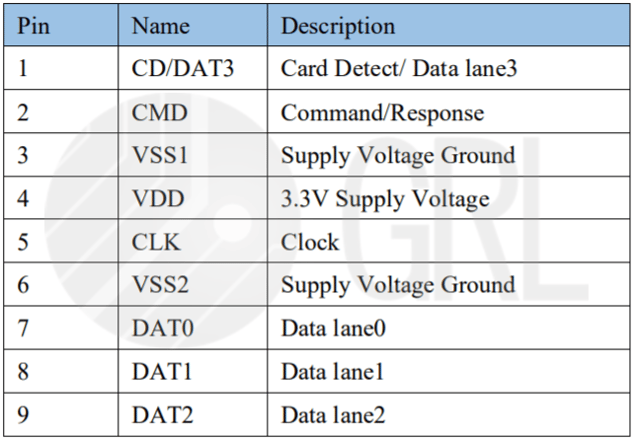

規格 4.0 匯流排介面為 UHS-II ,從原本的一排針腳升級成兩排針腳,原本的第一排針腳兼容預設、高速以及 UHS-I 的傳輸模式。而在 UHS-II 介面下所使用到的針腳可參考下方圖表 2,UHS-II 介面運用全雙工與半雙工的方式來進行訊號傳輸。可提供比 UHS-I 更快的匯流排速,訊號傳輸時有兩條路線, 在全雙工模式 會向下分配一條路線(主機到記憶卡)另一條則向上分配至另一條路線(記憶卡到主機)此模式可以同時向兩個方向傳送數據包其傳輸數度為 (156MB/s),而半雙工是在傳輸數據時兩條路線為同方向,其傳輸速率是兩倍 (312MB/s) 。

圖 2

.png?width=321434&name=5%20(1).png)

表 2

接下來將介紹 SD Card 物理層(Physical Layer)測試:

UHS-I

訊號傳輸時 DATA 會因寫入讀取而有 Input timing 以及 Output timing,而 Clock 會是單一方向的 Input timing。透過量測 CLK 以及 DATA 的訊號驗證參數值是否符合 SD 協會所訂製的設計規範(Specification)則能確保產品訊號發送的品質。

Clock 訊號的時鐘閥值 Clock Threshold (V_CT) 定義為 0.975V,透過 V_CT 建立參考點可以得知 CLK 周期,如圖 4;Input High Voltage (V_IH) 與 Input Low Voltage (V_IL) 是由開發者在範圍內定義,V_IH 在 1.27V 到 2.00V 之間,V_IL 在 V_SS-0.30V 到 0.58V 之間,V_IH 與 V_IL 的區間可得到 CLK 的上升時間 Rise time (t_CR) 與下降時間fall time (t_CF)。若想確認訊號品質,讀者主要可以關注 CLK 的週期、上升時間、下降時間以及佔空比是否符合規範要求。

DATA 的訊號以 V_CT 為參考點在 V_IH (max) V_IL (min) 標記點位區間(圖 5)為 DATA 的建立時間 Set-up time (t_IS)以及保持時間 Hold-time (t_IH),從圖我們可以知道若工作電壓過小以及使用者定義的 V_IH,V_IL 值過大時會導致建立時間與保持時間所標記的區間變短,這會造成產品難以辨別邏輯準位,所以在量測 DATA 訊號的過程可以關注兩者之間的關係。

.png?width=919475&name=%E5%9C%96%E7%89%871%20(2).png)

圖 4 (出自 Physical Layer Specification)

.png?width=727021&name=%E5%9C%96%E7%89%872%20(1).png)

圖 5 (出自 Physical Layer Specification)

UHS-II

UHS-II 的物理層測試在全雙工的模式下並透過讓產品進入 Forward / Backward Loopback mode 來讓兩訊號對 (D0,D1) 皆可進行傳送測試 (Transmitter Test) 以及接收測試 (Receiver Test),傳送測試 (Tx) 用來確認產品發送訊號的品質,接收測試 (Rx) 則確認產品能夠正確解讀接收到訊號的能力。產品會在兩種資料傳輸率 (Data rate) 下量測,分別是 Range A 和 Range B,Range A 為 CLK 頻率(UHS-II 產品規範 26MHz~52MHz)x 15 資料傳輸率 390Mbps~780Mbps;Range B 為 CLK 頻率 x30 資料傳輸率 780Mbps~1560Mbps。

(1) 傳送測試 (Transmitter Test)

測試訊號對 D0 時會使用訊號產生器 (Signal Generator) 發送測試 pattern (CLK 和 PRBS 2^7-1) 到訊號對 D1,透過 forward loopback mode 產品 將 D1 接收的訊號轉由 D0 發出(圖 6)進入示波器將擷取到的波形進行分析測試。測試訊號對 D1 時則須讓產品進入Backward loopback mode,訊號則會由 D0 進入 D1 輸出至示波器(圖 7)。下表 3 為 Tx 分析項目與規範,讀者可以看到對於訊號的上升、下降時間有最低要求,而分差電壓與共模電壓的規範可知兩者的相位差與電壓大小也須在一定範圍。

.png?width=516663&name=%E5%9C%96%E7%89%873%20(3).png)

圖 6

.png?width=1058852&name=%E5%9C%96%E7%89%874%20(3).png)

圖 7

.png?width=392120&name=6%20(1).png)

表 3

(2) 接收測試 (Receiver Test)

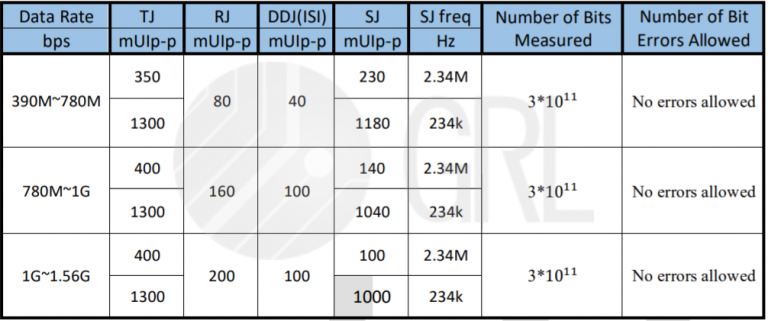

接收測試目的在於測試產品是否能夠準確接收訊號的能力,訊號在傳送的過程中會因線路、環境溫度等各樣因素導致訊號從發送端到達接收端有所衰減,接收端必須能在衰減的訊號下準確解讀訊號。因此在接收測試中儀器會在發送給產品的訊號源(使用 PRBS 2^7-1 test pattern)加入抖動頻率與抖動量,來模擬實際傳輸時的衰減,透過 Loopback mode 進行接收回傳至誤碼儀 (Error Detector) ,此過程不能有任何 bit error 產生。下表 4 為不同範圍傳輸率下 (390Mbps~1.56Gbps) 量測兩個抖動頻率點 (0.234MHz 和 2.34MHz) ,每點測試 3*10^11 個 bit 下規定所需加入的抖動量。

表 4

結論

SD Card UHS-I 介面支援工作電壓 1.8V 的 SDR25、SDR50、DR104、DDR50 傳輸模式,在物理層上量測 DATA, CLK 各參數值是否符合規範來確認訊號品質。UHS-II 兼容 UHS-I 傳輸模式外,全雙工的傳輸模式在 Range B 的狀態下訊號傳輸率可達 1560Mbps,在物理層的測試下透過讓產品進入 Loopback mode 來讓兩訊號對 (D0,D1) 皆可進行接收與發送的測試。希望透過本篇內容能讓讀者對 SD Card 有一個初步的概念。

參考文獻

- Part 1 UHS-II PHY Test Guideline Ver.1.00 Final 140714

- Part 1 Physical Layer Specification Ver5.10 Final 161101

- Part 1 UHS-II Addendum Ver1.02 Final 140528

- Format of SD Specification

文章下載

作者

GRL 台灣技術工程師 陳頌揚 Fred Chen

在GRL擁有超過三年測試經驗,熟悉DispalyPort, SD card, Thunderbolt function相關測試規範,協助客戶取得認證。GRL 技術文章作者及演講講師。

本文件中規格特性及其說明若有修改恕不另行通知。

發佈日期 2021/08/25 AN-210825-TW